## CI13082 数据手册

### 高性价比神经网络智能语音芯片

### • 脑神经网络处理器 (BNPU) • 复位和电源管理

- BNPU V3.5, 支持 DNN\TDNN\RNN\CNN 等 - 供电电压范围 3.6V~5.5V 神经网络及并行矢量运算,可实现高性能的 - 内置 PMU 电源管理单元 语音识别和通话降噪等功能

### • CPU 和存储器

- CPU 主频可达 210 MHz

- 内置 2MBytes Flash 存储器

- 内置 288KBytes SRAM

- 内置 256bit eFuse,可用于应用加密

### • Audio Codec

- 高性能低功耗 audio ADC, SNR ≥ 95dB

- 低功耗 audio DAC, SNR ≥ 95dB

#### PWM

- 支持 3 路 PWM 接口

### • GPI0

- 3 路高速 GPIO, 翻转频率可达 20MHz

- 2路 GPIO 支持 5V 电平通讯

- 内置上电复位 (POR)

- 内置电压检测 (PVD)

#### 时钟

- 内置 RC 振荡器

### • 通讯接口

- 1路 IIC 接口

- 1路 UART 接口,支持 5V 电平通讯,最高 支持 3Mbps 通讯速率

### • 定时器和看门狗

- 内置 2 组 32 位定时器和 1 个看门狗

## 目录

| 1 | 概述                   | 6  |

|---|----------------------|----|

|   | 1.1 功能描述             | 6  |

|   | 1.2 芯片规格             | 7  |

| 2 | 引脚图和功能描述             | 9  |

|   | 2.1 引脚图              | 9  |

|   | 2.2 管脚描述             | 10 |

|   | 2.3 复用功能             | 12 |

| 3 | 芯片接口描述               | 12 |

|   | 3.1 通用输入输出(GPIO)     | 12 |

|   | 3.1.1 简介             | 12 |

|   | 3.1.2 特性             | 12 |

|   | 3.2 通用异步收发传输器(UART)  | 13 |

|   | 3.2.1 简介             | 13 |

|   | 3.2.2 特性             | 13 |

|   | 3.2.3 时序图            | 13 |

|   | 3.3 脉冲宽度调制输出(PWM)    | 14 |

|   | 3.3.1 简介             | 14 |

|   | 3.3.2 特性             | 15 |

|   | 3.4 通用定时器(TIMER)     | 16 |

|   | 3.4.1 简介             | 17 |

|   | 3.4.2 特性             | 17 |

|   | 3.5 集成电路总线(IIC)      | 17 |

|   | 3.5.1 简介             | 17 |

|   | 3.5.2 特性说明           | 18 |

|   | 3.5.3 时序图            | 18 |

|   | 3.6 独立看门狗(IWDG)      | 19 |

|   | 3.6.1 简介             | 19 |

|   | 3.6.2 特性             | 19 |

|   | 3.7 多媒体音频编解码器(CODEC) | 19 |

|   | 3.7.1 简介             | 19 |

|   | 3.7.2 特性              | 20 |

|---|-----------------------|----|

|   | 3.8 增强型脉冲宽度调制输出(EPWM) | 20 |

|   | 3.8.1 简介              | 20 |

|   | 3.8.2 特性              | 20 |

|   | 3.8.3 配置值说明           | 21 |

|   | 3.8.4 计数模式            | 21 |

|   | 3.8.5 使用方法            | 21 |

| 4 | 电气特性                  | 23 |

| 5 | 封装信息                  | 24 |

| 6 | 订购信息                  | 25 |

| 7 | 应用方案                  | 26 |

|   | 7.1 应用参考电路图           | 26 |

|   | 7.2 其它应用注意事项          | 27 |

| 8 | 修订历史                  | 28 |

# 图片目录

| 冬 | 1  | :   | CI13082 功能框图          | 7    |

|---|----|-----|-----------------------|------|

| 图 | 2  | :   | CI13082 管脚顺序及定义图      | 9    |

| 图 | 3  | :   | 数据帧时序图 1              | . 14 |

| 图 | 4  | :   | 数据帧时序图 2              | . 14 |

| 图 | 5  | :   | 数据帧时序图 3              | . 14 |

| 图 | 6  | :   | 连续写数据操作时序图            | .18  |

| 图 | 7  | :   | 先写后读操作时序图             | . 19 |

| 图 | 8  | :   | IIC 读操作时序图            | . 19 |

| 图 | 9  | :   | 封装尺寸                  | .24  |

| 图 | 10 | )   | : CI1308X 典型应用方案参考电路图 | 26   |

| 图 | 11 | ۱ : | : 炉温曲线图               | .28  |

## 表格目录

| 表 | 1 | : | 管脚描述            | 10 |

|---|---|---|-----------------|----|

| 表 | 2 | : | I0 复用功能         | 12 |

| 表 | 3 | : | 电气特性表           | 23 |

| 表 | 4 | : | CI13082 芯片订购信息表 | 25 |

| 表 | 5 | : | CI1308X 升级模式表   | 27 |

| 表 | 6 | : | 修订历史            | 28 |

## 1 概述

### 1.1 功能描述

CI13082 是启英泰伦研发的新一代高性能神经网络智能语音芯片,集成了启英泰伦自研的脑神经网络处理器 BNPU V3.5 和 CPU 内核,系统主频可达 210MHz,内置高达 288KByte的 SRAM,集成 PMU 电源管理单元和 RC 振荡器,集成单通道高性能低功耗 Audio Codec 和多路 UART、IIC、PWM、GPIO 等外围控制接口。CI13082 芯片仅需少量电阻电容等外围器件,即可实现各类智能语音产品硬件方案,性价比极高。

CI13082 采用工业级设计标准,具有很好的环境可靠性,其工作温度范围- $40^{\circ}$ C~+85 $^{\circ}$ C,符合 MSL3 级湿敏等级、符合 IEC 61000-4-2 的 4KV 接触放电试验标准、符合 RoHS 和 REACH 环保标准。

CI13082 采用启英泰伦新一代 BNPU 技术,该技术支持 DNN\TDNN\RNN\CNN 等神经网络及并行矢量运算,可实现高性能语音识别、语音降噪等功能,具备强劲的环境噪声抑制能力。CI13082 方案还支持汉语、英语、日语等多种全球语言,可广泛应用于家电、照明、玩具、可穿戴设备、工业、汽车等产品领域,实现语音交互及控制和各类智能语音方案应用。

### 1.2 芯片规格

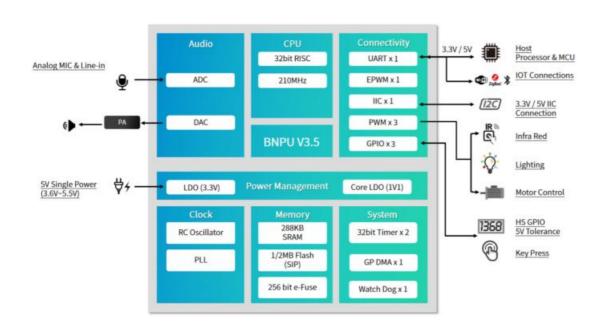

CI13082 功能框图如图 1 所示:

图 1: CI13082 功能框图

#### ■ 脑神经网络处理器 BNPU V3.5

- 采用启英泰伦新一代硬件 BNPU 技术,支持 DNN\TDNN\RNN\CNN 等神经网络及并行矢量运算,可实现高性能语音识别、语音降噪等功能

### ■ CPU

- 32 位高性能 CPU, 最高支持 210MHz 运行频率

### ■ 存储器

- 内置 288KB SRAM

- 内置 256bit eFuse

- 内置 2MB Flash

### ■ 音频接口

- 内置高性能低功耗 Audio Codec 模块,支持单路 ADC 采样和单路 DAC 播放

- 支持 Automatic Level Control (ALC)功能

- 支持 8kHz/16kHz/24kHz/32kHz/44.1kHz/48kHz 采样率

### ■ 电源管理单元 PMU

- 支持宽电源电压供电,供电范围 3.6V~5.5V

- 内置 2 路高性能 LDO 电路, 无需配置外置电源芯片, 应用方案仅需少量外围阻容器件

### ■ 时钟

- 内置 RC 振荡器

### ■ 外设和定时器

- 1路 UART 接口,支持最高 3M 波特率通讯

- 1路 IIC接口,可外接 IIC器件扩展

- 3 路 PWM 接口, 灯控和电机类的应用均可直接驱动

- 内置2组32bit timer

- 内置1组独立看门狗(IWDG)

#### ■ GPIO

- 支持 3 路 GPIO 口,可作为主控 IC 应用

- 每路 GPIO 口可配置中断功能,可配置上下拉状态

- 2路 GPIO 可通过外接 5V 上拉电阻直接支持 5V 电平通讯

### ■ 软件开发支持

- 提供完整软件开发包、应用方案示例、利用语音开发平台直接在线制作固件等支持,详情请访问: <a href="https://aiplatform.chipintelli.com">https://aiplatform.chipintelli.com</a>

### ■ 固件烧录和保护

- 支持 UART 升级和固件保护

### ■ ESD 性能

- 采用内部 ESD 增强设计,可通过 4KV 接触放电试验

#### ■ ROHS 和 REACH

- 采用环保材料,支持 RoHS 和 REACH 标准

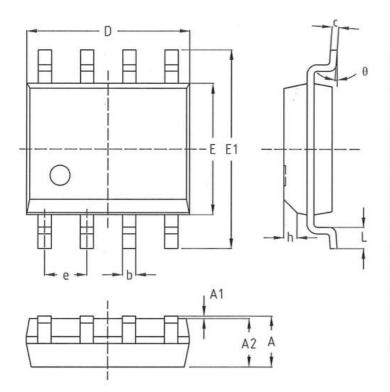

### ■ 封装和工作温度范围

- 封装形式: SOP8, 尺寸为长 4.9mm, 宽 6.0mm, 高 1.75mm

- 工作环境温度: -40℃~+85℃

## 2 引脚图和功能描述

## 2.1 引脚图

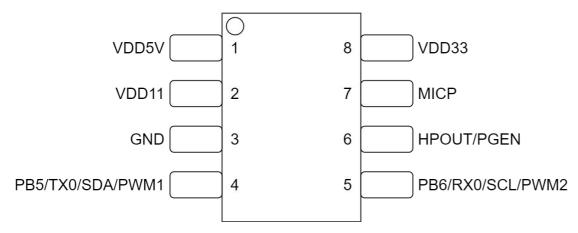

图 2: CI13082 管脚顺序及定义图

## 2.2 管脚描述

表 1: 管脚描述

| 管脚号 | 管脚名称  | 类型 | 是否支持<br>5V 电平 | 上电默认状态  | 管脚功能                                                                                                            |

|-----|-------|----|---------------|---------|-----------------------------------------------------------------------------------------------------------------|

| 1   | VIN5V | Р  | _             | _       | ● 供电电压输入,供电电压范围 3.6V~<br>5.5V<br>* Notel*                                                                       |

| 2   | VDD11 | Р  | _             | -       | ● LDO-1.1V 输出<br>● 内核 1.1V 供电输入<br>* Notel*                                                                     |

| 3   | GND   | P  | -             | _       | Ground                                                                                                          |

| 4   | PB5   | 10 | √             | IN, T+U | ● GPIO PB5 (上电默认状态) ● UARTO_TX ● IIC_SDA ● PWM1 ● PWMP                                                          |

| 5   | PB6   | 10 | √             | IN, T+U | ● GPIO PB6(上电默认状态) ● UARTO_RX ● IIC_SCL ● PWM2 ● PWMN                                                           |

| 6   | HPOUT | 0  | -             | -       | <ul> <li>DAC output</li> <li>PCO</li> <li>-</li> <li>-</li> <li>PWMO</li> <li>PGEN</li> <li>* Note2*</li> </ul> |

| 7   | MICP  | I  | -             | -       | <ul><li>Microphone P input</li><li>GPIO PC1</li><li>TX2</li><li>PWM3</li></ul>                                  |

| 8   | VDD33 | Р  | -             | -       | ● LDO-3.3V 输出<br>● 模拟 3.3V 供电输入<br>* Note1*                                                                     |

Notel 管脚需外接 4.7uF 电容

Note2 上电时该管脚为高电平,系统将进入编程模式

### 符号定义:

- I 输入

- 0 输出

- 10 双向

- P 电源或地

- T+D 三态下拉

- T+U 三态上拉

OUT 上电默认输出

IN 上电默认输入

所有 IO 均可配置驱动能力和上下拉状态。

### 2.3 复用功能

表 2: I0 复用功能

| Pin Name | Function1 | Function2 | Function3 | Function4 | Function5 | Function6 | Specific<br>Function |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|----------------------|

| PB5      | PB5       | UARTO_TX  | IIC_SDA   | PWM1      | PWMP      |           |                      |

| PB6      | PB6       | UARTO_RX  | IIC_SCL   | PWM2      | PWMN      |           |                      |

| PC0      | PC0       | _         | _         | PWMO      |           |           | D G DN               |

| *Note3*  | r co      |           |           | T WINO    |           |           | PGEN                 |

| PC1      | _         | PC1       | TX2       | PWM3      |           |           |                      |

Note3: HPOUT 与 PCO (PGEN) 管脚复用,内部默认下拉,上电后软件可配置其功能。当上电时系统检测到该管脚为高电平、且 UARTO 接口上有固件升级信号,则自动进入升级模式,此时可通过升级工具对芯片内部的 Flash 进行编程。若此时系统未检测到 UARTO 接口上有固件升级信号、或检测到 PCO 管脚的电压为低电平,都将进入正常工作模式。

## 3 芯片接口描述

## 3.1 通用输入输出(GPIO)

### 3.1.1 简介

GPIO(通用 IO 接口)是一种通用的输入输出端口,允许设备与外围硬件进行 电平信号交互,其既可以作为输入接收外部信号,也可以作为输出控制外围硬件。

### 3.1.2 特性

CI13082 支持多个可编程的输入/输出管脚(可由软件单独配置),每个 GPI0 端口都有相应的控制寄存器和配置寄存器,可单独打开或关闭每个 GPI0 管脚,实现对外围硬件的精准控制和状态监测。CI13082 芯片支持 2 组 GPI0 (GPI01、GPI02),其中 GPI02 对应的是芯片 PC 口,GPI01 对应的是芯片 PB 口。每组 GPI0 管脚分配请查看 2.2 管脚描述部分。

CI13082 提供 IO 输入输出状态查询接口、中断屏蔽接口、中断屏蔽查询接口、中断清除接口、中断状态查询接口、中断触发方式配置接口(可配置为: 低电平触发、高电平触发、上升沿触发、下降沿触发、双边沿触发)等,以满足不同的

应用场景和需求。

### 3.2 通用异步收发传输器(UART)

### 3.2.1 简介

UART 是一种通用异步串行通信数据接口,实现两个设备之间数据的接收和 发送,支持全双工通讯。接收端和发送端之间没有共享时钟信号,为保障通信可 靠性,通讯的两个设备需要设置相同的波特率和数据帧格式。

CI13082 支持 1 个 UART 控制器: UARTO。

### 3.2.2 特性

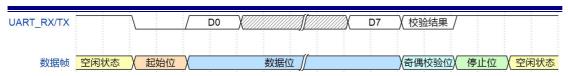

- 支持标准的 UART 协议,数据帧格式由起始位、数据位(长度可配置)、奇偶校验位(可选)和停止位(宽度可配置)四部分组成,支持波特率可配置。

- 总线处于空闲状态时,信号线为高电平状态。

- 起始位:用于标识传输数据帧的开始,每个数据帧以发送端输出一个比特宽度的低电平开始,通知接收端数据传输已启动;

- 数据位:传输的数据长度通过 UART\_LCR 寄存器可配置为 5~8 位,常用 8 位,位传输顺序为低位优先,先发送最低位 LSB 最后发送最高位 MSB;

- 奇偶校验位:通过 UART\_LCR 寄存器配置是否开启奇偶校验功能,通过 UART\_LCR 寄存器配置奇校验或偶校验。奇偶校验功能开启状态、数据位传输 完成后,可通过奇/偶校验检测数据传输是否错误;

- 停止位:用于标识传输数据帧的结束,每个数据帧以高电平结束,长度通过 UART\_LCR 寄存器可配置为 1、1.5、2 位;

删除[liuxiaofei]: )

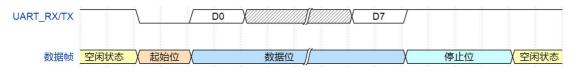

### 3.2.3 时序图

UART 数据传输 1 个数据帧(8 位数据位、奇偶校验位、1bit 停止位)的时序图如下:

图 3:数据帧时序图 1

UART 数据传输 1 个数据帧(起始位、7 位数据位、奇偶校验位、1. 5bit 停止位)的时序图如下:

图 4:数据帧时序图 2

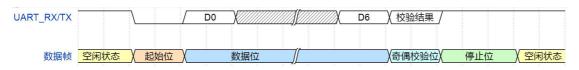

UART 数据传输 1 个数据帧(起始位、8 位数据位、无奇偶校验位、2bit 停止位)的时序图如下:

图 5: 数据帧时序图 3

UART 波特率设置越高,数据传输速度越快,但也会增加干扰和误码率。在设置波特率时,需要考虑通信双方串口硬件是否支持该波特率。若波特率设置过高,可能会导致数据传输不稳定。

支持最大 3Mbps 波特率,波特率可通过 UART\_I\_BRD 和 UART\_F\_BRD 寄存器配置。

### 3.3 脉冲宽度调制输出(PWM)

### 3.3.1 简介

PWM (Pulse Width Modulation) 是一种通过调节数字脉冲的占空比(高电平时间占整个周期的比例)来等效模拟信号电平的技术,广泛应用于电机控制、电源管理、LED 调光等领域。

CI13082 具有 4 个专用 PWM, 每个 PWM 输出信号的频率通过 TIMER\_SC 寄存器进行配置,每个 PWM 输出信号的占空比通过 TIMER\_SPWMC 寄存器进行配置,不 支持 100%占空比(常高),若需使用 100%占空比,通过配置 GPIO 来实现。

删除[liuxiaofei]: ,且每个专用 PWM 都有一组功能相同的寄存器以提高灵活性

删除[liuxiaofei]:

### 3.3.2 特性

- 计数时钟分频, 支持 1、2、4、16 分频, 通过 TIMER CFG 寄存器进行配置;

- 支持两个 32 位递减计数器;

- 可变占空比 PWM 脉冲宽度波形输出;

- 支持停止后输出电平极性通过 TIMER RESTART MD 寄存器配置;

### 3.4 通用定时器(TIMER)

### 3.4.1 简介

TIMER(通用定时器)是一个基于可配置分频器和多种计数方式 32 位递减计数器,在计数值达到 0 时触发一个定时事件,常用于在指定的时间间隔内反复触发指定窗口的定时器事件,可作为周期性中断发生器、事件计数器使用。CI13082具有 2 个相同的专用 TIMER: TIMER(0~TIMER1, 支持 TIMER 级联。

### 3.4.2 特性

• 支持三种计数模式,通过 TIMER\_CFG 寄存器进行配置:单周期计数模式、自动重装载计数模式、自由运行计数模式;

单周期计数模式: 定时器仅计数一个计数周期:

自动重装载计数模式: 计数器在每个计数结束时重新初始化:

自由运行计数模式: 计数值在每次计数结束时从 0xFFFFFFFF 循环到 0x00000000; \_

- 计数时钟分频,支持 1、2、4、16 分频,通过 TIMER CFG 寄存器进行配置;

- 32 位递减计数器,可读取计数器的实时值,通过 TIMER CC 寄存器进行读取;

- 支持级联模式配置,通过 TIMER CFGO 寄存器进行配置:

- <u>支持</u>计数<u>完成上报</u>中断;

### 3.5 集成电路总线(IIC)

### 3.5.1 简介

IIC 是一种双向双线同步串行总线,包括 SDA(串行数据线)和 SCL(串行时钟

删除[liuxiaofei]:每个专用 PWM 输出信号由 2 个周期寄存器 (TIMER\_SC 和 TIMER\_SPWMC)进行控制,计数器的计数值到 达相应的周期寄存器值时,输出最终的 PWM 信号,通过配置 2 个周期寄存器可以控制 PWM 输出信号的频率和占空比。每个 PWM 均有一个高/低电平比较器和选择器。 PWM 获取所选计数器的 32 位计数值,将其与寄存器 TIMER\_SPWMC 值和 0 进行比较,进而控制 PWM 输出信号的电平。

若 timer\_cnt==寄存器 TIMER\_SPWMC 的值,则 PWM 输出信号 pwm\_out 为 1;

若 timer\_cnt==0,则 PWM 输出信号 pwm\_out 为 0; 当计数器计数至 0 时,timer\_cnt 计数器会重新装载寄存器 TIMER\_SC 的值。timer\_cnt 计数器从寄存器 TIMER\_SC 配置的值开始递减,达到寄存器 TIMER\_SPWMC 配置的值时,PWM 输出信号由低置高,到达 0 时,PWM 输出信号由高置低,产生相应的 PWM 输出信号。

删除[liuxiaofei]: PWM

删除[liuxiaofei]: PWM

删除[liuxiaofei]: ,且每个专用 TIMER 都有一组功能相同的 寄存器以提高灵活性

删除[liuxiaofei]:每个 TIMER 模块由两个定时器单元组成,即 TIMER\_INIT\_0 和 TIMER\_INIT\_1,它们可作为两个独立的定时器也可组合成为一个单级联定时器,两个定时器单元进行级联工作时,TIMER\_INIT\_1 的时钟源可为级联模式下TIMER\_INIT\_0 的计数脉冲结束。

删除[liuxiaofei]:

PWM 脉冲宽度波形输出

删除[liuxiaofei]: 结束

删除[liuxiaofei]: 发生

线),SDA 和 SCL 管脚均为开漏输出。IIC 总线通常用于单个或多个主设备和单个或多个从设备之间通信,每个连接到总线上的设备都有一个唯一的地址,同一时刻仅允许有一个 master 主设备发起请求访问 slave 从设备。

CI13082 支持 1 个 IIC, 其数据帧格式通常由起始信号、地址信号、应答信号、数据信号和停止信号五部分组成,支持标准传输速率 100kbit/s 和快速传输速率 400kbit/s 两种模式。

### 3.5.2 特性说明

- SDA: 串行数据线,双向 I/O 线;

- SCL: 串行时钟线,由 master 提供;

- 支持 master 和 slave 模式可寄存器配置;

- master: 作为 master 主设备时启动总线传输数据,并产生时钟;

- slave: 作为 slave 从设备时被寻址的从设备,具有唯一地址;

- 起始信号: SCL 为高电平时, SDA 从高电平跳变至低电平,表示传输开始;

- 地址信号:支持 7 位寻址模式,包含 7bit 地址位和 1bit 读写位;

- 应答信号: ACK 接收成功, NACK 接受失败或传输结束;

- 数据信号:按 Byte 传输,先发送最高位 MSB 最后发送最低位 LSB;

- 停止信号: SCL 为高电平时, SDA 从低电平跳变至高电平, 表示传输结束;

- 总线传输速率可配置为标准-100kbit/s 和快速-400kbit/s;

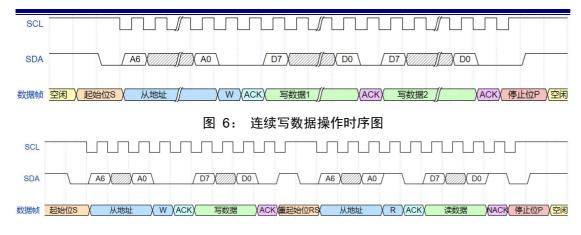

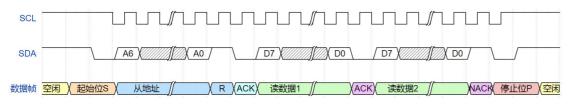

### 3.5.3 时序图

主设备通过产生 Start 起始条件来启动通信:在 SCL 为高电平时将 SDA 拉低,并通过 SCL 发送 8 个时钟脉冲用于传输 1 个 Byte,该 Byte 包含 7Bit 地址位和一 Bit 读/写位。若从设备的地址与传输的 7Bit 地址匹配,则产生应答信号。主设备和从设备可根据读/写位判断是发送还是接收数据,并根据应答位的逻辑电平判断是否结束数据传输。在数据传输过程中,SDA 仅在 SCL 为低时发生变化。一旦完成通信,主设备发送 STOP 停止条件来结束通信:在 SCL 为高电平时将 SDA 拉高。

图 7: 先写后读操作时序图

图 8: IIC 读操作时序图

### 3.6 独立看门狗(IWDG)

### 3.6.1 简介

IWDG 是一种硬件定时电路,主要用于监测系统由于工作异常而引发的故障并从故障中进行恢复。

### 3.6.2 特性

CI13082 支持 1 个 IWDG 模块, IWDG 是基于一个 32 位递减计数器, 计数器从装载值开始递减, 计数值计数到 0 时, 产生超时中断, 计数器重新加载装载值, 计数值再次计数到 0 时, 若超时中断未被清除,则 IWDG 将产生复位请求。可通过 SYS\_RESET\_CFG 寄存器配置复位域的范围。

### 3.7 多媒体音频编解码器(CODEC)

### 3.7.1 简介

CI13082 内置高性能低功耗音频 CODEC,支持一路 ADC、一路 DAC, MIC 输入的模拟信号经 MIC 增益,再经 PGA 放大。此 PGA 可通过 CODEC 本身的 ALC 控制, PGA 之后,还可通过数字增益进行放大。

### 3.7.2 特性

- DAC 支持最多 24bit, SNR 可达 90dB;

- ADC 支持最多 24bit, SNR 可达 90dB;

- 支持单端、差分的 MIC 输入和 line-in 输入;

- 支持 ALC 自动增益控制;

- 采样率支持: 8k/12k/16k/24k/32k/44.1k/48k;

### 3.8 增强型脉冲宽度调制输出(EPWM)

### 3.8.1 简介

EPWM(增强型脉冲宽度调制输出)是一种比普通 PWM 更为复杂的脉冲宽度调制技术,具有更多功能和配置选项。它能够实现反向、斩波、低电平或高电平指定相位等特殊功能,广泛应用于工业及消费类电子领域电源控制器件,例如电机控制、开关电源等。

每个 EPWM 由 2 路 PWM 输出组成,分别为引脚 PWMN 和 PWMP,且这一对 PWM 输出可单独当作普通 PWM 使用,或者互补 PWM 波输出,或者自定义的 PWM 输出。

### 3.8.2 特性

- 一个频率可控的 16-bit 计数器;

- 支持外部或软件通过 TBCTL 寄存器配置计数器的开始或结束;

删除[liuxiaofei]: 控制

● <u>支持</u>一对多<u>种</u>模式的 PWM 输出:中心对称 PWM 输出;边沿对称 PWM 输出;边沿对称 PWM 输出;边

● 支持初始相位通过 TBPHS 寄存器配置;

● 16-bit 死区时间, <u>支持</u>上升沿或下降沿的延迟时间<u>通过</u>DBRED 或 DBFED 寄存器配置; \_

● 外设刹车命令到来时,PWM输出通过TZSEL寄存器可配置为高电平、低电平、 高阻态: 删除[liuxiaofei]: 支持可调

删除[liuxiaofei]: 可单独调节

删除[liuxiaofei]: 可将

删除[liuxiaofei]: 强制成

删除[liuxiaofei]: 软件触发 CPU 中断

### 3.8.3 配置值说明

EPWM 的核心配置参数包括 TBPRD、ZERO、CMPA 和 CMPB。其中 TBPRD 定义了 PWM 波的周期长度,CMPA 和 CMPB 则用于设置占空比。通过配置这些参数,可控制 PWM 波的频率和占空比。

- TBPRD: 计数周期值(>0),配置宽度最大为16位,通过 AQCTLA或 AQCTLB寄存器配置计数到TBPRD值时产生拉高、拉低或不变等动作;

- ZERO: 计数周期值(=0), 通过 AQCTLA 或 AQCTLB 寄存器配置计数到 ZERO 值 时产生拉高、拉低或不变等动作;

- CMPA: 计数比较值 A, 配置宽度最大为 16 位, 通过 AQCTLA 或 AQCTLB 寄存器 配置计数到 CMPA 值时产生拉高、拉低或不变等动作:

- CMPB: 计数比较值 B, 配置宽度最大为 16 位, 通过 AQCTLA 或 AQCTLB 寄存器 配置计数到 CMPB 值时产生拉高、拉低或不变等动作;

### 3.8.4 计数模式

EPWM 支持三种计数模式: 递增模式、递减模式和增减模式。不同的计数模式适用于不同的应用场景。

- 递增模式: 计数器每个周期均是从 0 递增到 TBPRD。1 个 TBPRD 周期就能输出 1 周期 PWM, 支持通过 TBCTR 寄存器配置;

- 递减模式: 计数器每个周期均是从 TBPRD 递减到 0。1 个 TBPRD 周期就能输出 1 周期 PWM, 支持通过 TBCTR 寄存器配置;

- 增减模式: 计数器在奇数周期从 0 向 TBPRD 递增,在偶数周期从 TBPRD 递减到 0。2 个 TBPRD 周期就能输出 1 周期 PWM,支持通过 TBCTR 寄存器配置;

### 3.8.5 使用方法

EPWM 可通过配置输出多种不同的波形,例如 50%占空比 PWM 波、低电平占空比 PWM 波等。若要得到所需波形,首先需要配置 TBPRD、CMPA、CMPB 的值,并指定 其计数模式,再配置计数器计数到 TBPRD、ZERO、CMPA、CMPB 值时分别产生什么 动作,最终就能输出所需的波形。在该过程中,允许配置 CMPA= CMPB,或者 CMPA> CMPB,或者 CMPA<CMPB。

## 4 电气特性

表 3: 电气特性表

| 符号                                     | 描述                                                        | 最小值       | 典型值  | 最大值        | 单位                     |

|----------------------------------------|-----------------------------------------------------------|-----------|------|------------|------------------------|

| VIN5V                                  | 芯片供电输入 *Note4*                                            | 3.6       | 5.0  | 5. 5       | V                      |

| AVDD                                   | 3. 3V电源                                                   | 2.97      | 3. 3 | 3. 63      | V                      |

| VDD11                                  | 1. 1V电源                                                   | 0.99      | 1. 1 | 1.21       | V                      |

| $V_{{\scriptscriptstyle \mathrm{IH}}}$ | 输入高电平<br>(3.0V ≤VDD33 ≤ 3.6V)                             | 0.7×VDD33 | -    | VDD33+0.3  | V                      |

| $V_{\scriptscriptstyle \mathrm{IL}}$   | 输入低电平<br>(3.0V ≤ VDD33 ≤ 3.6V)                            | -0.3      | -    | 0. 3×VDD33 | V                      |

| $V_{oL}$                               | 输出低电平 @I <sub>OL</sub> = 12mA                             | _         | ı    | 0.4        | V                      |

| $V_{\mathrm{OH}}$                      | 输出高电平 @I <sub>M</sub> = 20mA                              | 2.4       | =    | _          | V                      |

| I5V-10                                 | 5V耐压I0口输出3.3V时驱动电流                                        | 20        | =    | 33         | mA                     |

| I 3v3-10                               | 3.3V耐压I0口输出3.3V时驱动电流                                      | 14        | -    | 24         | mA                     |

| $\Sigma$ IVDD                          | 芯片所有10总电流之和                                               | _         | -    | 90         | mA                     |

| Pde                                    | 芯片采用5V供电且VDD11采用外部<br>供给1.1V状态,正常识别时5V电源<br>的总功耗(TA=25°C) | 40        | -    | 90         | mW                     |

| Pdi                                    | 芯片采用5V供电且系统采用内部<br>LD0供电,正常识别时5V输入的总功<br>耗(TA=25°C)       | 125       | -    | 255        | mW                     |

| RC振荡<br>器精度<br>*Note5*                 | Ta: -40°C∼+85°C                                           | -1.5      | =    | +1.5       | %                      |

| Тор                                    | 芯片工作环境温度                                                  | -40       | -    | +85        | $^{\circ}\!\mathbb{C}$ |

| Tst                                    | 芯片储存环境温度                                                  | -55       | -    | +150       | °C                     |

Note4:要求纹波小于 300mVp-p。

Note5:半导体技术原理及特性的原因,芯片内置的 RC 振荡器在高低温环境中,其振荡频率精度会产生一定的温漂(±1.5%),CI13082 内置波特率自适应电路,可支持在高低温环境中芯片与上位机的正常通讯。若应用方案要求芯片的时钟需要非常精确,请采用我司配置有外置晶振的芯片及相应的应用方案。

## 5 封装信息

|              | 机械万        | マサ/mm          |            |  |  |

|--------------|------------|----------------|------------|--|--|

|              | Dimer      | nsions         | 100        |  |  |

| 字符<br>SYMBOL | 最小值<br>MIN | 典型值<br>NOMINAL | 最大值<br>MAX |  |  |

| Α            | -          | -              | 1.75       |  |  |

| A1           | 0.10       | 0.15           | 0.25       |  |  |

| A2           | 1.35       | 1.45           | 1.55       |  |  |

| b            | 0.35       | -              | 0.50       |  |  |

| c            | 0.19       | -              | 0.25       |  |  |

| D            | 4.80       | 4.90           | 5.00       |  |  |

| Ε            | 3.80       | 3.90           | 4.00       |  |  |

| E1           | 5.80       | 6.00           | 6.20       |  |  |

| e 1.27 BSC   |            |                |            |  |  |

| h            | 0.30       | -              | 0.50       |  |  |

| L            | 0.50       | -              | 0.80       |  |  |

| θ            | 0.         | _              | 8°         |  |  |

图 9:封装尺寸

## 6 订购信息

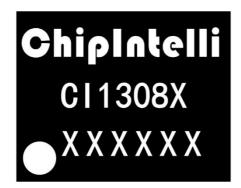

CI13082 芯片封装 MRAK 如下图,第一行为公司 LOG,第二行为芯片型号,第三行为生产批次号,左下角圆点为1 脚标识。

芯片型号定义如下:

CI13082 芯片订购信息见表 5-1。

表 4: CI13082 芯片订购信息表

| 产品型号    | 封装形式 | 基本包装 | 管装数量   | 出厂标准包装 | 标准包装数量                |

|---------|------|------|--------|--------|-----------------------|

| CI13082 | SOP8 | 管装   | 100pcs | 盒装     | 20000pcs<br>(200 管/盒) |

### 7 应用方案

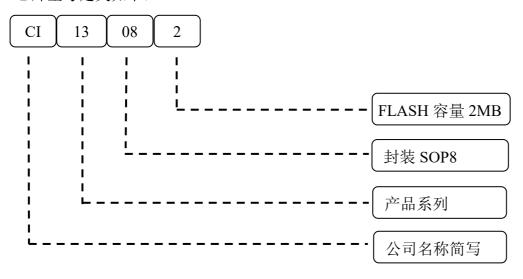

### 7.1 应用参考电路图

CI13082 芯片需少量外围仅器件,即可开发出支持各类语音应用的终端产品方案。 CI13082 支持单麦克风单端输入。应用方案设计可根据方案所需的功能、功耗和成本等需求 因素,选择适合的电路设计方案。

以下以 CI13082 的典型应用方案为例,介绍应用方案设计的要点和注意事项

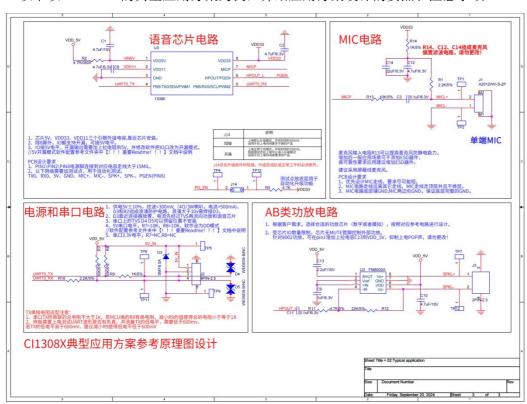

图 10: CI1308X 典型应用方案参考电路图

上图为包括 CI13082 在内的 CI1308X 系列芯片,单麦克风单端输入和功放输出的典型应用方案的参考设计电路图,该设计不局限于匹配某个具体的终端产品。应用方案的设计应基于适配上位机终端产品的原则,根据终端产品的功能和性能需求,前往启英泰伦文档中心和AI 平台下载参考原理图和参考 PCB 图。文档中心链接 https://document.chipintelli.com

应用方案设计时若需预留板级升级功能,可以将 UARTO 引脚以插座或测试点的方式引出,以便于 PCB 板贴片完成后通过 UARTO 烧写或升级固件。

CI13082 的 HPOUT/PGEN 管脚在芯片内部预置有下拉电阻,上电时系统将检测该引脚是 否被外部上拉电阻拉高为 3.3V 高电平,若是高电平且检测 UARTO 引脚有外部输入的升级信 号,系统即进入升级模式。若该引脚外部未接上拉电阻,芯片上电时可跳过升级模式检测环 节直接进入正常启动模式,以实现系统的快速开机。若应用方案有快速开机需求,可将 HPOUT/PGEN 管脚引出,预留一跳线,然后接一个 4.7K Ω 的电阻上拉到 VDD33。该设计状态下系统上电时为正常功能启动模式,开机时间可缩短为 350ms 左右。若此时需要在线升级,可通过短接跳线或短接跳线两端的测试点将 PGEN 管脚拉为 3.3V 高电平,即可通过 UARTO口升级;若应用方案无快速开机需求,可通过 4.7K Ω 电阻将 PGEN 直接拉高。具体实施方案请参照参考应用图原图或咨询我司的 FAE,PGEN 两种工作模式如下表:

| PG_EN 工作模式图示                                | J14 安装情<br>况 | PG_EN 高低电<br>平 | 开机时间  |

|---------------------------------------------|--------------|----------------|-------|

| TP4 TP13 TP13 TP13 TP13 TP13 TP13 TP13 TP13 | 短接           | 高电平,升级模式       | 850ms |

| TP4 TP13 TP13 TP13 TP13 TP13 TP13 TP13 TP13 | 开路           | 低电平,工作模式       | 350ms |

表 5: CI1308X 升级模式表

CI13082 芯片无 MICBIAS 脚,麦克风供电采用外部 3.3V,推荐采用图 10 中的供电设计,由 R14、C12、C14 构成的滤波电路不可更改。

CI13082 仅支持单端麦克风输入,推荐采用图 10 中的麦克风设计,且线长小于 20 厘米。该典型应用方案的功放配置为 AB 类功放,推荐采用 8002 系列功放。若不需要语音播报功能,可去除该部分电路以降低方案成本。功放 MUTE 功能请参考参考图 10。

CI13082 的 UART 口可支持 5V 电平通讯。应用方案若需外接 5V 通讯电平,推荐采用图 6-1 中的串口设计,在 UARTO 的 RX 和 TX 引脚外围增加 5V 上拉电阻即可,无需配置电平转换电路。

### 7.2 其它应用注意事项

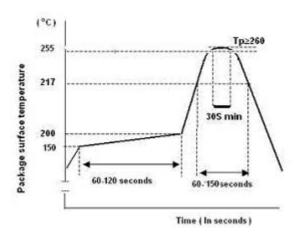

1. CI13082 采用无铅环保材料制造,SMT 焊接时请按照无铅标准设置炉温和时间参数。如

下图

图 11: 炉温曲线图

2. CI13082 的取用、搬运、生产加工等过程需注意采取防静电措施,其包装需采用防静电材料。

## 8 修订历史

表 6: 修订历史

| 修订版本 | 修订内容       | 修订日期       |

|------|------------|------------|

| 1.0  | 初始版本       | 2024.06.19 |

| 1.1  | 1、增加接口部分描述 | 2025.07.03 |

| _    |            |            |

- 启英泰伦保留对本说明书的解释权和更改权,如有更改恕不另行通知!客户在应用设计前应获取 最新版本资料,并验证相关信息是否准确和完整。

- 任何半导体产品在特定条件下都有发生失效或故障的可能,芯片应用方有责任在使用本产品进行系统设计和整机制造时,遵守安全标准并采取安全防护措施,以避免可能的产品失效造成人身伤害或财产损失!

- 启英泰伦将竭诚为客户提供更好的产品和更优质的服务!